## Z87000/Z87L00

# Spread Spectrum Controllers

**Customer Procurement Specification**

DS96WRL0501

## Z87000/Z87L00 Spread Spectrum Controllers

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

©2001 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

## Z87000/Z87L00

## SPREAD SPECTRUM CONTROLLERS

#### **FEATURES**

| Device | ROM<br>(KWords) | RAM*<br>(Words) | I/O<br>Lines | Package<br>Information     |

|--------|-----------------|-----------------|--------------|----------------------------|

| Z87000 | 12              | 512             | 32           | 84-Pin PLCC<br>100-Pin QFP |

| Z87L00 | 12              | 512             | 32           | 100-Pin QFP                |

Note: \*General-Purpose

- Transceiver/Controller Chip Optimized for Implementation of 900 MHz Spread Spectrum Cordless Phone

- Adaptive Frequency Hopping

- Transmit Power Control

- Error Control Signaling

- Handset Power Management

- Support of 32 kbps ADPCM Speech Coding for High Voice Quality

- DSP Core Acts as Phone Controller

- Zilog-Provided Embedded Transceiver Software to Control Transceiver Operation and Base Station-Handset Communications Protocol

- User-Modifiable Software Governs Phone Features

- Transceiver Circuitry Provides Primary Cordless Phone Communications Functions

- Digital Downconversion with Automatic Frequency Control (AFC) Loop

- FSK Demodulator

- FSK Modulator

- Symbol Synchronizer

- Time Division Duplex (TDD) Transmit and Receive Buffers

- On-Chip A/D and D/A to Support 10.7 MHz IF Interface

- Bus Interface to Z87010 ADPCM Processor

- Static CMOS for Low Power Consumption

- 3.0V to 3.6V, -20°C to +70°C, Z87L00 4.5V to 5.5V, -20°C to +70°C, Z87000

- 16.384 MHz Base Clock

#### **GENERAL DESCRIPTION**

The Z87000/Z87L00 FHSS Cordless Telephone Transceiver/Controllers are expressly designed to implement a 900 MHz frequency hopping spread spectrum cordless telephone compliant with United States FCC regulations for unlicensed operation. The Z87000 and Z87L00 are distinct 5V and 3.3V versions, respectively, of the device. For the sake of brevity, all subsequent references to the Z87000 in this document also apply to the Z87L00, unless specifically noted.

The Z87000 supports a specific cordless phone system design that uses frequency hopping and digital modulation to provide extended range, high voice quality, and low system costs. The Z87000 uses a Zilog 16-bit fixed-point two's complement static CMOS Digital Signal Processor core as the phone and RF section controller. The Z87000's DSP core processor further supports control of the RF section's frequency synthesizer for frequency hopping and the generation of the control messages needed to coordinate incorporation of the phone's handset and base station.

## **GENERAL DESCRIPTION** (Continued)

Additional on-chip transceiver circuitry supports Frequency Shift Keying modulation/demodulation and multiplexing/demultiplexing of the 32 kbps voice data and 4 kbps command data between handset and base station. The Z87000 provides thirty-two I/O pins, including four wake-up inputs and two CPU interrupt inputs. These programmable I/O pins allow a variety of user-determined phone features and board layout configurations. Additionally, the pins may be used so that phone features and interfaces

are supported by an optional microcontroller rather than by the Z87000's DSP core.

In combination with an RF section designed according to the system specifications, Zilog's Z87010/Z87L10 ADPCM Processor, a standard 8-bit PCM telephone CODEC and minimal additional phone circuity, the Z87000 and its embedded software provide a total system solution.

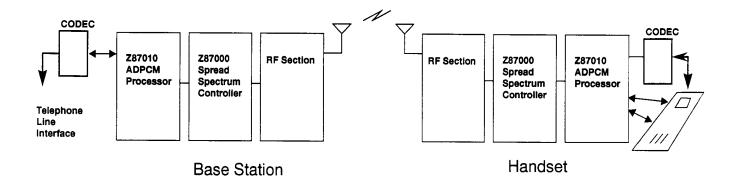

Figure 1. System Block Diagram of a Z87000/Z87010 Based Phone

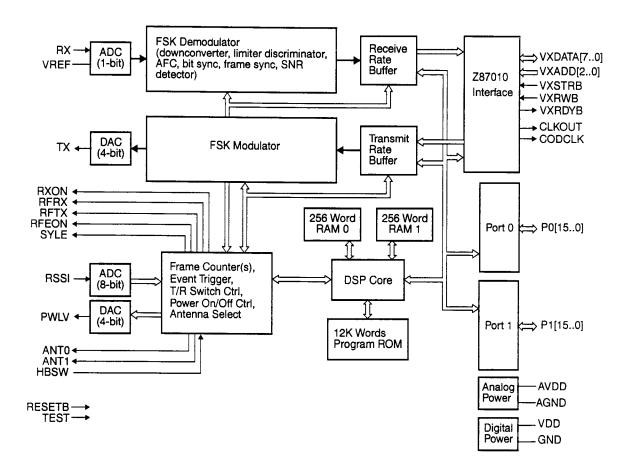

Figure 2. Z87000 Functional Block Diagram

## PIN DESCRIPTION

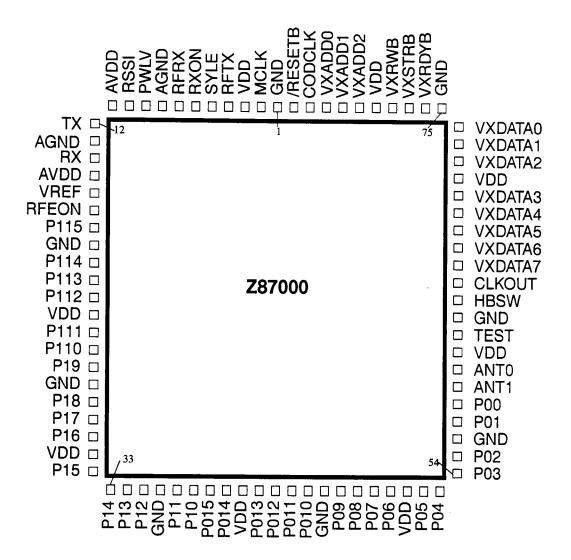

Figure 3. 84-Pin PLCC ROM Pin Configuration (Z87000 only)

Table 1. 84-Pin PLCC Pin Description Summary

| Pin Number                                              | Symbol           | Function                               | Direction    |  |

|---------------------------------------------------------|------------------|----------------------------------------|--------------|--|

| 1,19,27,36,46,<br>56,63,75                              | GND              | Ground                                 | _            |  |

| 2                                                       | MCLK             | Master clock (16.384 MHz)              | Input        |  |

| 3,23,31,41,51,<br>61,71,79                              | V <sub>DD</sub>  | Digital                                | _            |  |

| 4                                                       | RFTX             | RF transmit switch control             | Output       |  |

| 5                                                       | SYLE             | RF synthesizer load enable             | Output       |  |

| 6                                                       | RXON             | Demodulator "on" indication            | Output       |  |

| 7                                                       | RFRX             | RF receive switch control              | Output       |  |

| 8,13                                                    | AGND             | Analog ground                          | _            |  |

| 9                                                       | PWLV             | RF transmit power level                | Output       |  |

| 10                                                      | RSSI             | RF receive signals strength indicator  | Input        |  |

| 11,15                                                   | AV <sub>DD</sub> | Analog V <sub>DD</sub>                 | -            |  |

| 12                                                      | TX               | Analog transmit IF signal              | Output       |  |

| 14                                                      | RX               | Analog receive IF signal               | Input        |  |

| 16                                                      | V <sub>REF</sub> | Analog reference voltage for RX signal | Output       |  |

| 17                                                      | RFEON            | RF module on/off control               | Output       |  |

| 18,20,21,22,24,<br>25,26,28,29,30,<br>32,33,34,35,37,38 | P115             | General-purpose                        | Input        |  |

| 59,60                                                   | ANT1             | RF diversity antenna control           | Input/Output |  |

| 62                                                      | TEST             | Main test mode control                 | Input        |  |

| 64                                                      | HBSW             | Handset/Base Control                   | <del>-</del> |  |

| 65                                                      | CLKOUT           | Clock output to ADPCM Processor        | Output       |  |

| 76                                                      | VXRDYB           | ADPCM processor ready signal           | Output       |  |

| 77                                                      | VXSTRB           | ADPCM processor data strobe            | Input        |  |

| 78                                                      | VXRWB            | ADPCM read/write control               | Input        |  |

| 80,81,82                                                | VXADD2           | ADPCM processor address bus            | Input        |  |

| 83                                                      | CODCLK           | Clock output to codec                  | Output       |  |

| 84                                                      | /RESETB          | Reset signal                           | Input        |  |

## PIN DESCRIPTION (Continued)

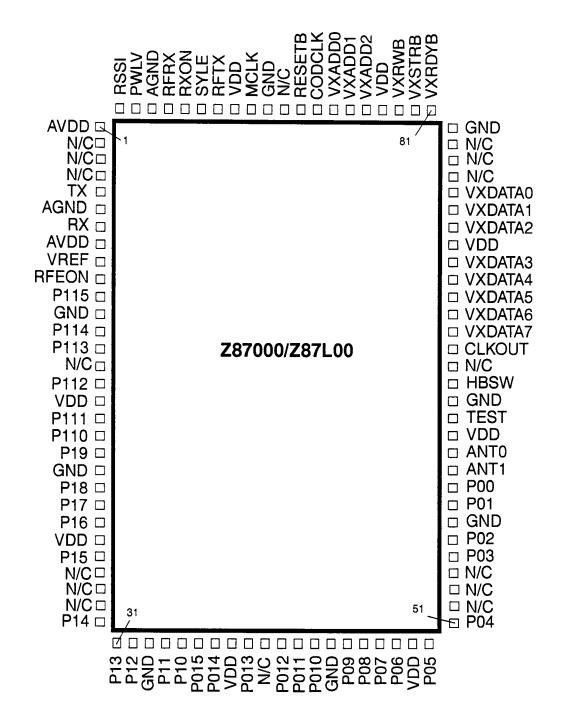

Figure 4. 100-Pin QFP Pin Configuration

Table 2. 100-Pin QFP Pin Configuration

| No                                                      | Symbol           | Function                               | Direction    |

|---------------------------------------------------------|------------------|----------------------------------------|--------------|

| 1,8                                                     | AV <sub>DD</sub> | Analog V <sub>DD</sub>                 | _            |

| 2,3,4,15,27,28,                                         | N/C              | No connection                          | <del>-</del> |

| 29,40,52,53,54,                                         |                  |                                        |              |

| 66,77,78,79,90                                          |                  |                                        |              |

| 5                                                       | TX               | Analog transmit IF signal              | Output       |

| 6,98                                                    | AGND             | Analog ground                          | _            |

| 7                                                       | RX               | Analog receive IF signal               | Input        |

| 9                                                       | VREF             | Analog reference voltage for RX signal | _            |

| 10                                                      | RFEON            | RF module on/off control               | Output       |

| 11,13,14,16,18,<br>19,20,22,23,23,<br>26,30,31,32,34,35 | P1[150]          | General-purpose I/O port 0             | Input        |

| 17,25,38,49,62,<br>73,84,93                             | $V_{DD}$         | Digital                                | _            |

| 36,37,39,41,42,<br>43,45,46,47,48,<br>50,51,55,56,58,59 | P0[150]          | General-purpose I/O port 0             | Input        |

| 60,61                                                   | ANT[10]          | RF diversity antenna control           | Input/Output |

| 53                                                      | TEST             | Main test mode control                 | Input        |

| 65                                                      | HBSW             | Handset/bast control                   | Input        |

| 57                                                      | CLKOUT           | Clock output to ADPCM processor        | Output       |

| 58,69,70,71,72,<br>74,75,76                             | VXDATA[7]        | ADPCM processor data bus               | Input        |

| 31                                                      | VXRDYB           | ADPCM processor ready signal           | Output       |

| 32                                                      | VXSTRB           | ADPCM processor data strobe            | Input        |

| 33                                                      | VXRWB            | ADPCM processor read/write control     | Input        |

| 35,86,87                                                | VXADD[20]        | ADPCM processor address bus            | Input        |

| 38                                                      | CODCLK           | Clock output to codec                  | Output       |

| 39                                                      | /RESETB          | Reset signal                           | Input        |

| 92                                                      | MCLK             | Master clock input (16.384 MHz)        | Input        |

| )4                                                      | RFTX             | RF transmit switch control             | Output       |

| 95                                                      | SYLE             | RF synthesizer load enable             | Output       |

| 96                                                      | RXON             | Demodulator "on" indication            | Output       |

| 97                                                      | RFRX             | RF receive switch control              | Output       |

| 99                                                      | PWLV             | RF transmit power level                | Input        |

| 100                                                     | RSSI             | RF receive signal strength indicator   | Input        |

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                             | Parameter                | Min  | Max                   | Units |

|------------------------------------|--------------------------|------|-----------------------|-------|

| V <sub>DD</sub> , AV <sub>DD</sub> | DC Supply<br>Voltage(1)  | -0.5 | 7.0                   | V     |

| V <sub>IN</sub>                    | Input Voltage(2)         | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| V <sub>OUT</sub>                   | Output Voltage(3)        | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| T <sub>A</sub>                     | Operating<br>Temperature | -20  | +70                   | °C    |

| T <sub>STG</sub>                   | Storage<br>Temperature   | -65  | +150                  | °C    |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended period may affect device reliability.

#### Notes:

- 1. Voltage on all pins with respect to GND.

- 2. Voltage on all inputs WRT VDD

- 3. Voltage on all outputs WRT VDD

#### STANDARD TEST CONDITIONS

The electrical characteristics listed below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pins. Standard test conditions are as follows:

- 3.0V < V<sub>DD</sub> < 3.6V (Z87L00)

- 4.5V < V<sub>DD</sub> < 5.5V (Z87000)

- GND = 0V

- $T_A = -20 \text{ to } +70 \text{ °C}$

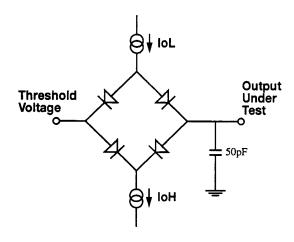

Figure 5. Test Load Diagram

## **RECOMMENDED OPERATING CONDITIONS**

Table 3.  $5V \pm 0.5V$  Operation (Z87000)

| Symbol                             | Parameter                                    | Min                                     | Max                   | Units |

|------------------------------------|----------------------------------------------|-----------------------------------------|-----------------------|-------|

| V <sub>DD</sub> , AV <sub>DD</sub> | Supply Voltage                               | 4.5                                     | 5.5                   | V     |

| V <sub>IH</sub>                    | Input High Voltage                           | 2.0                                     | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>                    | Input Low Voltage                            | GND -0.3                                | 0.8                   | V     |

| Гон                                | Output High Current                          |                                         | -2.0                  | mA    |

| I <sub>OL1</sub>                   | Output Low Current                           |                                         | 4.0                   | mA    |

| OL2                                | Output Low Current, Ports (limited usage, 1) |                                         | 12.0                  | mA    |

| T <sub>A</sub>                     | Operating Temperature                        | -20                                     | +70                   | °C    |

| Notes:                             | 1111111                                      | *************************************** |                       |       |

#### Notes:

Table 4.  $3.3V \pm 0.3V$  Operation (Z87L00)

| Symbol          | Parameter                                    | Min                 | Max                  | Units |

|-----------------|----------------------------------------------|---------------------|----------------------|-------|

| $V_{DD}$        | Supply Voltage                               | 3.0                 | 3.6                  | V     |

| V <sub>IH</sub> | Input High Voltage                           | 0.7 V <sub>DD</sub> | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage                            | GND -0.3            | 0.1 V <sub>DD</sub>  | V     |

| Он              | Output High Current                          |                     | -1.0                 | mA    |

| OL1             | Output Low Current                           |                     | 2.0                  | mA    |

| OL2             | Output Low Current, Ports (limited usage, 2) |                     | 6.0                  | mA    |

| T <sub>A</sub>  | Operating Temperature                        | -20                 | +70                  | °C    |

<sup>1.</sup> Maximum 3 pins total from P0[15..0] and P1[15..0]

<sup>1.</sup> Maximum 3 pins total from P0[15..0] and P1[15..0]

## DC ELECTRICAL CHARACTERISTICS

Conditions for DC characteristics are corresponding operating conditions, and standard test conditions, unless otherwise specified.

Table 5.  $5V \pm 0.5V$  Operation (Z87000)

| Symbol           | Parameter                     | Test Condition                            | Min | Max | Units |

|------------------|-------------------------------|-------------------------------------------|-----|-----|-------|

| V <sub>OH</sub>  | Output High Voltage           | V <sub>DD</sub> min, I <sub>OH</sub> max  | 2.4 |     | V     |

| V <sub>OL1</sub> | Output Low Voltage            | V <sub>DD</sub> min, I <sub>OL1</sub> max |     | 0.6 | V     |

| V <sub>OL2</sub> | Output Low Voltage, Ports (1) | V <sub>DD</sub> min, I <sub>OL2</sub> max |     | 1.2 | V     |

| ſĹ               | Input Leakage                 | $V_{IN} = 0V, V_{DD}$                     | -2  | 2   | μА    |

| lcc              | Supply Current                |                                           |     | 80  | mA    |

| I <sub>CC2</sub> | Standby Mode Current (2)      |                                           |     | 4   | mA    |

#### Notes:

- 1. Maximum 3 pins total from P0[15..0] and P1[15..0]

- 2. 2.3 mA typical at 25°C, 5 volts.

Table 6.  $3.3V \pm 0.3V$  Operation (Z87L00)

| Symbol               | Parameter                    | Test Condition                            | Min | Max | Units |

|----------------------|------------------------------|-------------------------------------------|-----|-----|-------|

| V <sub>OH</sub>      | Output High Voltage          | V <sub>DD</sub> min, I <sub>OH</sub> max  | 1.6 |     | V     |

| $\overline{V_{OL1}}$ | Output Low Voltage           | V <sub>DD</sub> min, I <sub>OL1</sub> max |     | 0.4 | V     |

| V <sub>OL2</sub>     | Output Low Voltage, Ports(1) | V <sub>DD</sub> min, I <sub>OL2</sub> max |     | 1.2 | V     |

| <b>I</b> L           | Input Leakage                | $V_{IN} = 0V, V_{DD}$                     | -2  | 2   | μА    |

| Icc                  | Supply Current               |                                           |     | 55  | mA    |

| I <sub>CC2</sub>     | Standby Mode Current(2)      |                                           | 1.4 |     | mA    |

- 1. Maximum 3 pins total from P0[15..0] and P1[15..0]

- 2. 1.6 mA typical at 25°C, 3.3 volts.

## **ANALOG CHARACTERISTICS**

Table 7. 1-Bit ADC (Temperature: -20/+70°C)

| Parameter                        | Minimum                      | Typical                       | Maximum                       | Units |

|----------------------------------|------------------------------|-------------------------------|-------------------------------|-------|

| Resolution                       | -                            | 1                             | -                             | bit   |

| Power dissipation                | 0.54                         | 1.0                           | 2.75                          | mW    |

| Power discipation Ctan made      | (70°c)                       | (40°c)                        | (-20°c)                       |       |

| Power dissipation, Stop mode     | 0.06<br>(70°c)               | 0.2<br>(40°c)                 | 1.1<br>(-20°c)                | mW    |

| Sample frequency                 | •                            | 8.192                         | -                             | MHz   |

| Sample window(1)                 | 29                           | 31                            | 33                            | ns    |

| Bandwidth                        | -                            | 60                            | -                             | MHz   |

| Supply Range(=AV <sub>DD</sub> ) |                              |                               |                               |       |

| Z87L00                           | 3.0                          |                               | 3.6                           | V     |

| Z87000                           | 4.5                          |                               | 5.5                           | V     |

| Acquisition time                 | 2                            | 3                             | 8                             | ns    |

| Settling time                    | 8                            | 10                            | 18                            | ns    |

| Conversion time                  | 4                            | 6                             | 18                            | ns    |

| Aperture delay                   | 2                            | 3                             | 8.5                           | ns    |

| Aperture uncertainty(2)          | •                            | -                             | 0.5                           | ns    |

| Input voltage range (p-p)        | 800                          | 1000                          | 1200                          | mV    |

| Reference voltage                |                              |                               |                               |       |

| Z87L00                           | 1.7 (AV <sub>DD</sub> = 3V)  | 1.9 (AV <sub>DD</sub> = 3.3V) | 2.1 (AV <sub>DD</sub> = 3.6V) | V     |

| Z87000                           | 2.7 (AV <sub>DD</sub> =4.5V) | $3.0 (AV_{DD} = 5V)$          | $3.3 (AV_{DD} = 5.5V)$        | V     |

| Input resistance                 | 10                           | 18                            | 25                            | KOhm  |

| Input capacitance                | -                            | 10                            | -                             | pF    |

#### Notes:

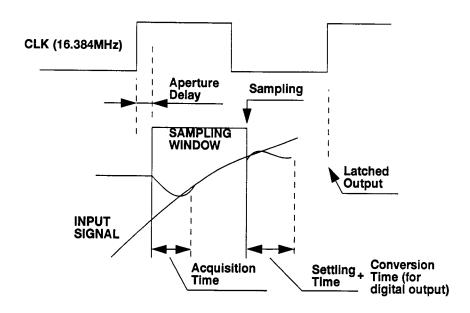

Window of time while input signal is applied to sampling capacitor; see next figure. Uncertainty in sampling time due to random variations such as thermal noise.

## **ANALOG CHARACTERISTICS** (Continued)

Figure 6. 1-Bit ADC Definition of Terms

Table 8. 8-bit ADC (Temperature -20/+70°C)

| Parameter                         | Minimum | Typical            | Maximum | Units |

|-----------------------------------|---------|--------------------|---------|-------|

| Resolution                        | •       | 6                  | -       | bit   |

| Integral non-linearity            | •       | 0.5                | 1       | LSB   |

| Differential non-linearity        | -       | -                  | 0.5     | LSB   |

| Power Dissipation (peak)          |         | 35                 | 70      | mW    |

| Sample window                     | 5       | -                  | 120     | ns    |

| Bandwidth                         | -       | •                  | 2       | Msps  |

| Supply Range (=AV <sub>DD</sub> ) |         |                    |         |       |

| Z87L00                            | 3.0     | 3.3                | 3.6     | ٧     |

| Z87000                            | 4.5     | 5.0                | 5.5     | V     |

| Input voltage range               |         | 0-AV <sub>DD</sub> |         | V     |

| Conversion time                   | 0.5     | -                  | -       | μѕ    |

| Aperture delay                    | 2       | 3                  | 8.5     | ns    |

| Aperture uncertainty              | -       | -                  | 1       | ns    |

| Input resistance                  | -       | 25                 | -       | Kohm  |

| Input capacitance                 | -       | 10                 | -       | pF    |

<sup>8-</sup>bit ADC only tested for 6-bit resolution.

Table 9. 4-bit DAC (Temperature: -20/+70°C)

|                                                 | •       | • • •                                       |         |       |

|-------------------------------------------------|---------|---------------------------------------------|---------|-------|

| Parameter                                       | Minimum | Typical                                     | Maximum | Units |

| Resolution                                      | -       | 4                                           | -       | bit   |

| Integral non-linearity                          | -       | 0.25                                        | 0.5     | LSB   |

| Differential non-linearity                      | -       | 0.25                                        | 1       | LSB   |

| Settling time (1/2 LSB)                         | -       | -                                           | 22.5    | ns    |

| Zero error at 25°C                              | -       | 1                                           | 2       | mV    |

| Conversion time (input change to output change) | 14      | 19                                          | 76      | ns    |

| Power dissipation, 25 pF load                   | 1.2     | 20                                          | 24.1    | mW    |

|                                                 | (70°c)  | (40°c)                                      | (-20°c) |       |

| Power dissipation, 25 pF load, Stop mode        | 0.18    | 1.0                                         | 1.1     | mW    |

|                                                 | (70°c)  | (40°c)                                      | (-20°c) |       |

| Conversion time (input change to output change) | 14.5    | 19.1                                        | 75.8    | ns    |

| Rise time (full swing)                          | 11      | 15                                          | 71      | ns    |

| Output slew rate                                | 8       | 67                                          | 96      | V/µs  |

| Output voltage range                            | -       | 0.2 AV <sub>DD</sub> to 0.6AV <sub>DD</sub> | -       | V     |

| Supply Range (=AV <sub>DD</sub> )               |         |                                             |         |       |

| Z87L00                                          | 3.0     | 3.3                                         | 3.6     | V     |

| Z87000                                          | 4.5     | 5.0                                         | 5.5     | V     |

| Output load resistance                          |         | 330                                         |         | Ohm   |

| Output load capacitance                         | -       | 25                                          | =       | pF    |

|                                                 |         |                                             |         |       |

## INPUT/OUTPUT PIN CHARACTERISTICS

All digital pins (all pins except  $V_{DD}$ ,  $AV_{DD}$ , GND, AGND,  $V_{REF}$ , RX, TX, RSSI and PWLV) have an internal capacitance of 5 pF.

The RX analog input pin has an input capacitance of 10 pF.

The RSSI analog input pin has an input capacitance of 10 pF.

## **AC ELECTRICAL CHARACTERISTICS**

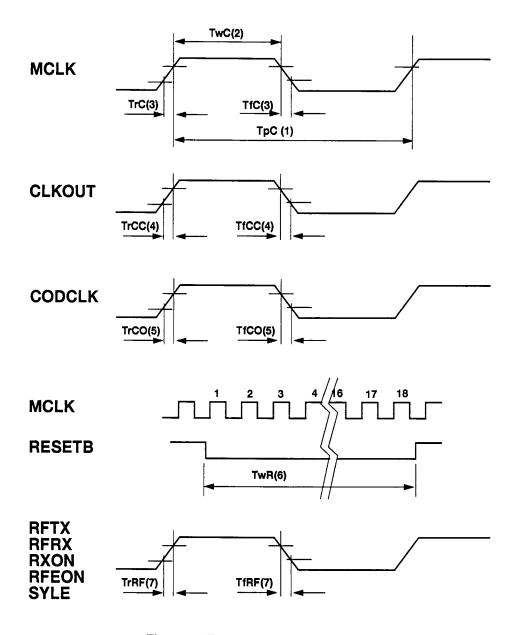

## Clocks, Reset and RF Interface

Table 10. Clocks, Reset and RF Interface

| No. | Symbol     | Parameter                             | Min | Max | Units |

|-----|------------|---------------------------------------|-----|-----|-------|

| 1   | ТрС        | MCLK input clock period (1)           | 61  | 61  | ns    |

| 2   | TwC        | MCLK input clock pulse width          | 20  | 40  | ns    |

| 3   | TrC, TfC   | MCLK input clock rise/fall time       |     | 15  | ns    |

| 4   | TrCC, TfCC | CLKOUT output clock rise/fall time    | 2   | 6   | ns    |

| 5   | TrCO, TfCO | CODCLK output clock rise/fall time    | 2   | 6   | ns    |

| 6   | TwR        | RESETB input low width                | 18  |     | TpC   |

| 7   | TrRF, TfRF | RF output controls rise/fall time (2) | 2   | 6   | ns    |

- 1. MCLK is 16.384 MHz ± 25 ppm

- 2. RF Controls are RFTX, RFRX, RXON, RFEON, SYLE.

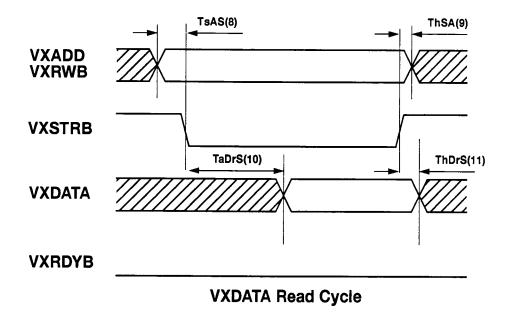

## **ADPCM Processor Interface**

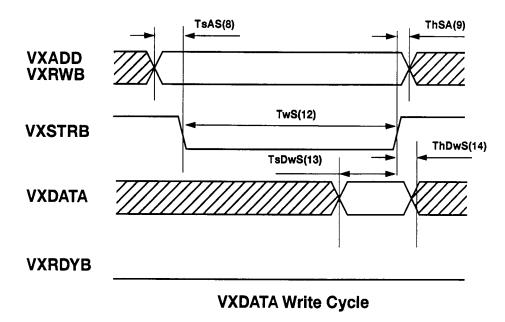

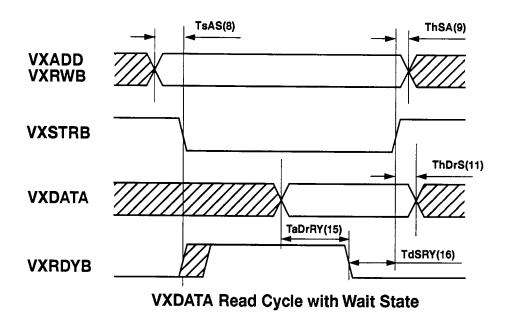

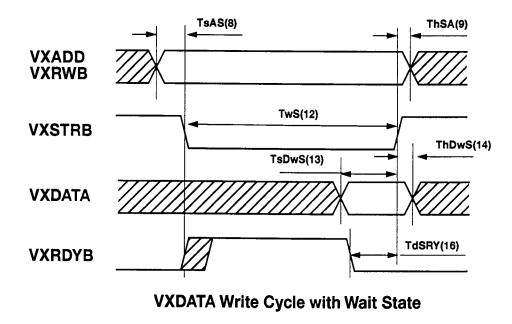

The Z87000 is a peripheral device for the ADPCM Processor. The interface from the Z87000 perspective is composed of an input address bus, a bidirectional data bus, strobe and read/write input control signals and a ready/wait output control signal.

READ CYCLES refer to data transfers from the Z87000 to the ADPCM Processor.

WRITE CYCLES refer to data transfers from the ADPCM Processor to the Z87000.

Table 11. Read Cycles

| Signal Name | Function                           | Direction ADPCM Proc. to Z87000 |  |

|-------------|------------------------------------|---------------------------------|--|

| VXADD[20]   | Address Bus                        |                                 |  |

| VXDATA[70]  | Data Bus                           | Bidirectional                   |  |

| VXSTRB      | Strobe Control Signal              | ADPCM Proc. to Z87000           |  |

| VXRWB       | Read/Write Control Signal          | ADPCM Proc. to Z87000           |  |

| VXRDYB      | Ready Control Signal Z87000 to ADP |                                 |  |

Table 12. Write Cycles

| No. | Symbol | Parameter                                          | Min | Max    | Units |

|-----|--------|----------------------------------------------------|-----|--------|-------|

| 8   | TsAS   | Address, Read/Write setup time before Strobe falls | 10  |        | ns    |

| 9   | ThSA   | Address, Read/Write hold time after Strobe rises   | 3   |        | ns    |

| 10  | TaDrS  | Data read access time after Strobe falls           |     | 30 (1) | ns    |

| 11  | ThDrS  | Data read hold time after Strobe rises             | 8.5 | 40 (2) | ns    |

| 12  | TwS    | Strobe pulse width                                 | 20  | ***    |       |

| 13  | TsDwS  | Data write setup time before Strobe rises          | 10  |        | ns    |

| 14  | ThDwS  | Data write hold time after Strobe rises            | 3   |        | ns    |

| 15  | TaDrRY | Data read valid before Ready falls                 | 22  |        | ns    |

| 16  | TdSRY  | Strobe high after Ready falls                      | 0   |        | ns    |

- 1. Requires wait state on ADPCM Processor read cycles

- 2. Requires no write cycle directly following read cycle on ADPCM Processor

## **AC TIMING DIAGRAMS**

Figure 7. Transceiver Output Signal

Figure 8. Read/Write Cycle Tlmings

## AC TIMING DIAGRAMS (Continued)

Figure 9. Read/Write Cycle Timing with Wait State

#### **Pre-Characterization Product:**

The product represented by this CPS is newly introduced and Zilog has not completed the full characterization of the product. The CPS states what Zilog knows about this product at this time, but additional features or non-conformance with some aspects of the CPS may be found,

either by Zilog or its customers in the course of further application and characterization work. In addition, Zilog cautions that delivery may be uncertain at times, due to start-up yield issues.

© 1996 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 FAX 408 370-8056

Internet: http://www.zilog.com